Компания Rambus, специализирующаяся на разработке высокоскоростных интерфейсов передачи данных, сообщает об очередном проекте Terabyte Bandwidth Initiative (TBI), в рамках которого перед инженерами поставлена задача разработки шины с пропускной способностью свыше одного терабайта/с. Такое решение должно найти широкое применение в качестве интерфейса передачи данных в многоядерной процессорной архитектуре. На данный момент «теоретическая» составляющая уже готова, и дело за созданием рабочего образца интегральной микросхемы.

Новый высокоскоростной интерфейс представляет собой объединенные в единую систему 16 DRAM-каналов передачи данных, общая пропускная способность которых составляет 1024 Гбайт/с. Таким образом, каждый канал способен передавать до 64 Гбайт данных за секунду.

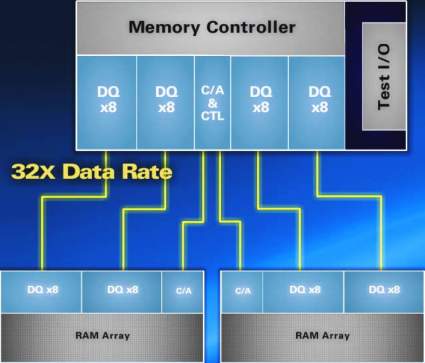

Для достижения таких высоких скоростей разработчикам пришлось использовать систему тактирования FlexLink, которая повышала входящую частоту в 500 МГц в 32 раза. При этом было решено использовать архитектуру памяти Fully Differential Memory Architecture (FDMA) и технологию FlexPhase, обеспечивающую невысокий уровень ошибок при столь высокой скорости передачи данных.

Планируется, что технология TBI найдет своей применение в вычислительных системах в 2010 – 2011 годах, когда заметно возрастет потребность высокоскоростных шинах для передачи данных между памятью и многоядерным процессором. Однако пока разработчики не имеют не только готового продукта, с которым можно выйти на мировой рынок, но и рабочего прототипа для иллюстрации возможностей своей технологии.